# EE115A Analog Circuits

## Homework 6

Due date: **12/4/2025**

**Note:**

- Please provide enough calculation process to get full marks.

- Please submit your homework to Gradescope (code **J62G3D**) in PDF version.

- It's highly recommended to write every exercise on a single sheet of page.

- Late submissions will have points deducted according to the penalty policy.

- Please use English only to complete the assignment, solutions in Chinese are not allowed.

- Plagiarizer will get zero points.

- The full score of this assignment is 100 points.

### Exercise 1. (25pt)

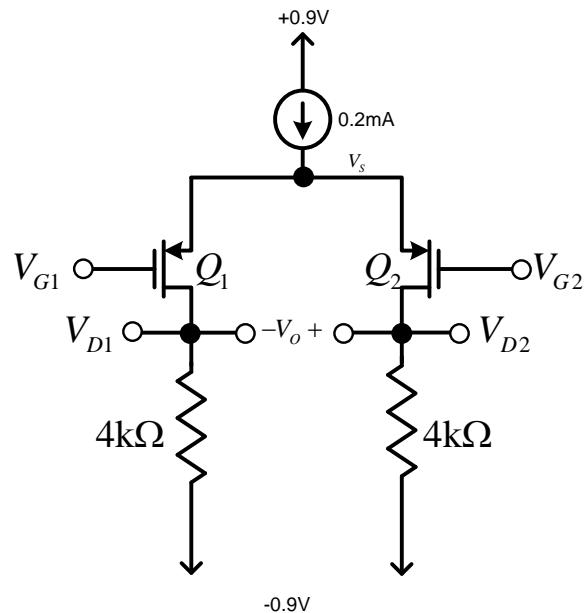

For the PMOS differential amplifier shown in Fig. P1, let  $V_{tp} = -0.4$  V and

$k'pW/L = 5 \text{ mA/V}^2$ . Neglect channel-length modulation.

(a) For  $V_{G1} = V_{G2} = 0$  V, find  $|V_{ov}|$  and  $V_{SG}$  for each of Q1 and Q2. Also find  $V_s$ ,  $V_{D1}$ ,

$V_{D2}$ , and  $V_o$ .

(b) If the current source requires a minimum voltage of 0.2 V, find the input common-mode range.

Fig. P1

## Exercise 2. (25pt)

Consider the differential amplifier specified in Problem &2 with  $G_2$  grounded

and  $V_{G1} = V_{id}$ . Let  $V_{id}$  be adjusted to the value that causes  $i_{D1} = 0.09\text{mA}$  and

$i_{D2} = 0.07\text{ mA}$ . Find the corresponding values of  $V_{GS2}$ ,  $V_s$ ,  $V_{GS1}$  and hence  $V_{id}$ .

What is the difference output voltage  $V_o$ ? What is the voltage gain

$V_o / V_{id}$ ? What value of  $V_{id}$  results in  $i_{D1} = 0.07\text{ mA}$  and  $i_{D2} = 0.09\text{ mA}$ ?

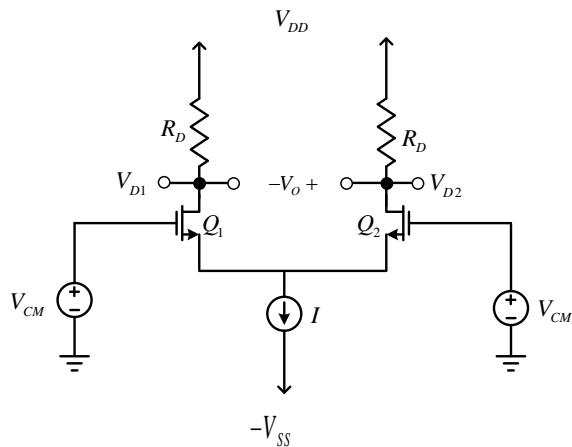

**Problem &2: (This question does not require an answer)**

For an NMOS differential pair with a common-mode voltage  $V_{CM}$  applied, as

shown in Fig.P2, let  $V_{DD} = V_{SS} = 1.0\text{ V}$ ,  $k'n = 0.4\text{ mA/V}^2$ ,  $(W/L)_{12} = 10$ ,  $V_{tn} = 0.4\text{ V}$ ,  $I = 0.16\text{ mA}$ ,  $R_D = 5\text{ k}\Omega$ , and neglect channel-length modulation.

- (a) Find  $V_{ov}$  and  $V_{GS}$  for each transistor.

- (b) For  $V_{CM} = 0$ , find  $V_s$ ,  $i_{D1}$ ,  $i_{D2}$ ,  $V_{D1}$ ,  $V_{D2}$ , and  $V_o$ .

- (c) Repeat (b) for  $V_{CM} = +0.4\text{ V}$ .

- (d) Repeat (b) for  $V_{CM} = -0.1\text{ V}$ .

- (e) What is the highest value of  $V_{CM}$  for which  $Q_1$  and  $Q_2$  remain in saturation?

- (f) If current source  $I$  requires a minimum voltage of  $0.2\text{ V}$  to operate properly, what is the lowest value allowed for  $V_s$  and hence for  $V_{CM}$ ?

- (g) What is the input common-mode range

Fig. P2

### Exercise 3. (25pt)

**Note:** This question requires simulation. Please note that you need to use **Multisim** for simulation and provide the simulation circuit and simulation results in your answer.

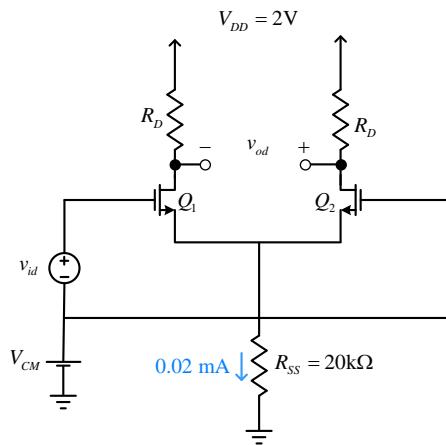

The differential amplifier in Fig. P3 utilizes a resistor  $R_{SS}$  to establish a 0.02-mA dc bias current.

Note that this amplifier uses a single 2-V supply and thus the dc common-mode voltage cannot be zero. Transistors Q1 and Q2 have  $k_n W/L = 1 \text{ mA/V}^2$ ,  $V_t = 0.4 \text{ V}$ , and  $\lambda = 0$ .

- (a) Find the required value of  $V_{CM}$ .

- (b) Find the value of  $R_D$  that results in a differential gain  $A_d$  of 15 V/V.

- (c) Determine the dc voltage at the drains.

- (d) Determine the single-ended-output common-mode gain  $\Delta V_{DI}/\Delta V_{CM}$ . (Hint: You need to take  $1/g_m$  into account.)

- (e) Use the common-mode gain found in (d) to find the change in  $V_{CM}$  that results in Q1 and Q2 entering the triode region.

Fig. P3

### Exercise 4. (25pt)

A current-mirror-loaded NMOS differential amplifier is fabricated in a technology for which  $|V_A| = 6V/\mu m$ . All the transistors have  $L = 0.5 \mu m$ . If the differential-pair transistors are operated at  $V_{ov} = 0.2 V$ , what open-circuit differential gain is realized?